Substantially faster main memory chips for computers are on the horizon after an electronics industry consortium with more than a hundred members agreed on the first standards specifications for the new technology.

Version 1.0 of the Hybrid Memory Cube specification [PDF] was published overnight by the eponymous consortium that counts electronics giants ARM, Hewlett-Packard, IBM, Micron, Samsung, Hynix and Xilinx as members.

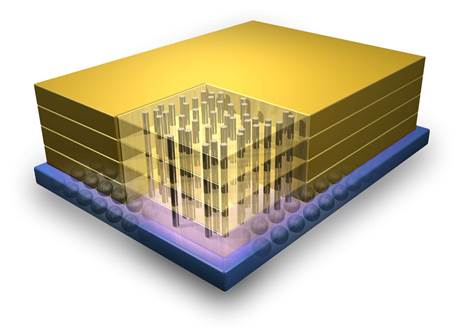

The new memory chips are expected to go into production in the middle of this year and feature a stacked design with short reach and ultra-short reach interconnects that helps achieve high data rates of 10, 12.5 or 15 gigabit/s in the current specification.

This is expected to be going up to 28 gigabit/s in the next generation specification due out next year, the HMCC says.

Memory bandwidth is a performance bottleneck for high-performance computers and networking equipment, which require more memory bandwidth than the current generation of DRAM can provide.

HMCC says the new 3D memory can break through the "memory wall" or bandwidth bottleneck with increased density and lower power consumption as well as improved performance. Overall, the new modules can provide fifteen times the bandwidth of current DDR3 memory while taking up only a tenth of the space. the HMCC claims.

Servers for high-performance and cloud computing are expected to use the new HMCC technology, which when assembled in dynamic random access memory (DRAM) modules provides aggregate bandwith of up to 160 gigabytes per second.

_(39).jpg&w=100&c=1&s=0)

iTnews Executive Retreat - Data & AI Edition

iTnews Executive Retreat - Data & AI Edition

.png&w=120&c=1&s=0) iTnews Cloud Covered Breakfast Summit

iTnews Cloud Covered Breakfast Summit

iTnews State of Security Breakfast

iTnews State of Security Breakfast

The 2026 iAwards

The 2026 iAwards

.jpg&w=120&c=1&s=0) Integrate 2026

Integrate 2026

_(1).jpg&h=140&w=231&c=1&s=0)